来源:半导体所

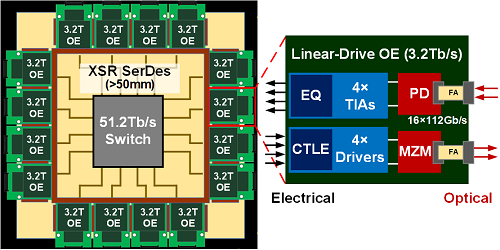

数据密集型人工智能计算的爆炸式增长对数据中心的互连带宽提出更高要求。传统可插拔光模块难以满足新型51.2T以太网交换机对功耗和外形尺寸的要求,必须采用功耗较高的基于DSP的光收发机来补偿每通道的损耗。通过将紧凑型光引擎紧密集成到交换机封装中,板载金属线大部分被光纤取代,从而节省了信号功率并提高了前面板的带宽密度(如图1所示,每个3.2T的光引擎在封装中实现了光纤通道直接连接到交换机封装边缘)。与此同时,集成的共封装光学器件(CPO)用嵌入了连续时间线性均衡器(CTLE)的线性驱动器和放大器取代了 DSP,从而简化了光收发机。近年来,这种线性直驱CPO逐渐受到关注,因为它能显著降低功耗、成本和延迟。

中国科学院半导体研究所半导体物理实验室刘力源、祁楠研究员团队,长期专注于高速硅基光电集成收发机的研究,并取得了一系列成果。团队成功构建了由时钟数据恢复电路(CDR)、分布式CMOS驱动器与集总分段式马赫-增德尔调制器(MZM)构成的单路50Gb/s光电发射机(JSSC,2022),和由硅光探测器(PD)、跨阻放大器(TIA)与CDR构成的单路50Gb/s光电接收机 (TCAS-I,2023)。近期,刘力源、祁楠研究员团队与国家信息光电子创新中心总经理肖希合作,在4×112Gb/s线性直驱硅基光电集成收发机研究领域取得新进展,构建了了用于线性直驱CPO的4×112 Gb/s硅基光电混合集成收发机组件。

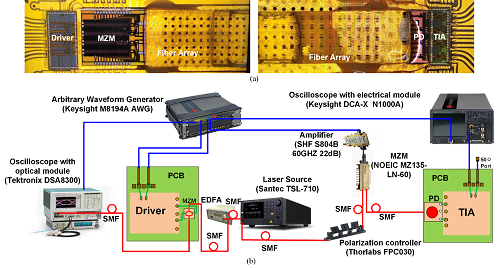

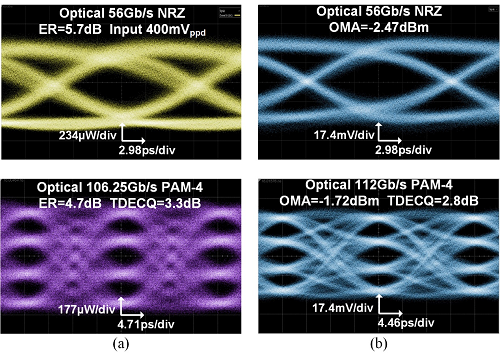

该研究团队通过四通道集电极开路的驱动器与阵列化的行波MZM协同设计,实现了高带宽和高驱动效率,还提出了一种二阶混合无源-有源CTLE,用于补偿高达12dB的非线性信道损耗。此外,该团队还提出了一种带有T-π输入网络和级联内嵌式CTLE的线性TIA,可在保持平坦带内频率响应的同时提高带宽。该驱动器和TIA采用180nm SiGe BiCMOS工艺实现,测量结果显示其带宽超过35GHz。通过将驱动器与MZM、TIA与PD共同封装,构建了完整的硅基光电集成收发机前端(图2为光发射机和光接收机的封装照片,图3为实验结果)。电光调制和光电接收均可实现400G速率的应用需求。光发射机实现了5dB的光消光比和4.8pJ/bit的功耗效率,而光接收机实现了67dB的跨阻增益和2.95pJ/bit的功耗效率。

该成果由半导体所博士生刘翰、半导体所祁楠研究员、国家信息光电子创新中心肖希等共同完成,并得到了国家重点研发计划、国家自然科学基金和北京市科技计划项目的资助。

图1 集成在交换机中线性直驱光引擎

图2 混合集成光收发机封装照片

图3 光收发机NRZ和PAM-4的测试结果